上一篇介紹如何安裝Intel Quartus及建立第一個專案:這篇文章要練習一下如何繪製區塊圖Block Diagram/Schematic File(簡稱BDF)。

到這裡已經完成簡單的and和or邏輯電路圖,可以選擇[File]→ [Save]存檔。

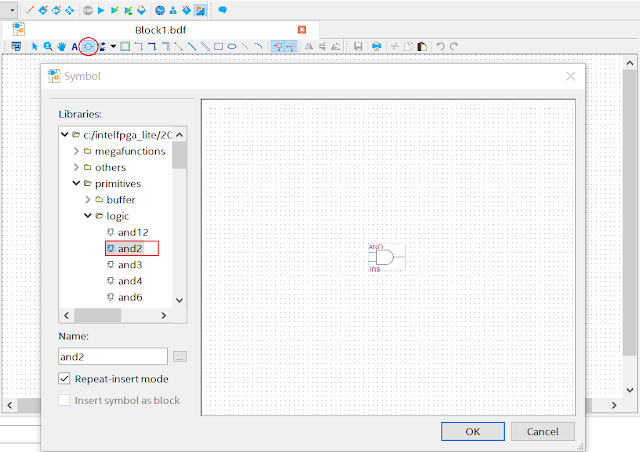

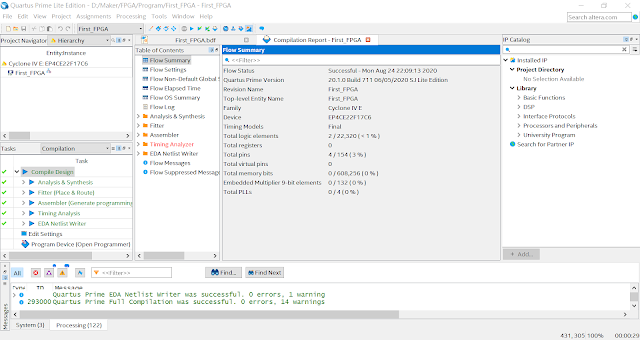

接著進行編譯,可以按下圖中央上方紅圈處的往右箭頭(Compilation)或按下 Ctrl + L 進行編譯,成功或失敗可以在下方視窗看到結果,如果成功就會看到以下畫面:

到這裡已經完成電路圖的繪製,接著練習如何使用波形檢視結果。

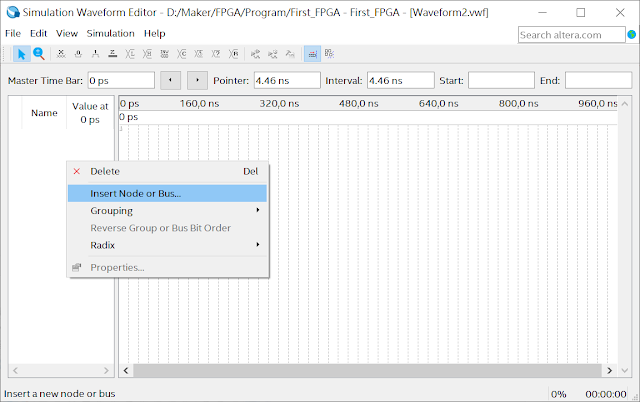

按下 OK 後出現以下視窗,可在左方紅框處按滑鼠右鍵,選擇[Insert Node or Bus]:

除了使用上述的方法外,還可以在功能選單按下 [Edit] → [Insert] → [Insert Node or Bus],出現下圖中右方的一個小視窗, 按下下圖1的 Node Finder ,出現左方小視窗,按下標示2的 List ,出現稍早編譯好的邏輯圖Input跟Output變數名稱。按下標示3的 >> 將變數加進已選擇的視窗內,按下 OK 回到小視窗,再按一次 OK 。

按下 OK 後出現以下視窗,如要放大或縮小時間間距,可以用 Ctrl + 滑鼠滑輪進行縮放。

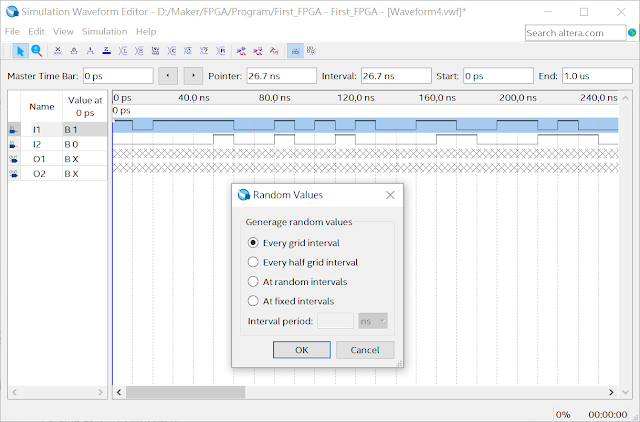

對I1及I2進行高低電位設定,在這裡使用的是隨機訊號Random Values,可以看到以下畫面是視窗設定的選項及呈現的結果。

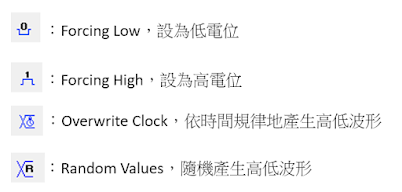

常用的設定圖示,有以下幾種:

設定完成後,要呈現波形的結果,可以在上方選單[Simulation]下拉,選擇[Run Functional Simulation],進入編譯視窗。正常應該會編譯會成功,因我用的是v20.1試用版,第一次執行時,出現以下錯誤畫面:

錯誤說明 -novopt 選項在不久將來要被移除,雖然不知道這是什麼設定?需要修改編譯參數,可以到上方選單[Simulation]下拉,選擇[Simulation Settings],看到以下視窗。將藍色標示的字刪除,按下Save存檔,再次執行 [Run Functional Simulation]就可以成功了。

編譯成功得到的結果如下圖,可以看到 and閘 及 or閘的結果:

首先新增一個繪製區塊電路圖的底稿,選擇 [File] → [New],出現以下視窗,選擇「Block Diagram/Schematic File」,按下 OK 繼續。

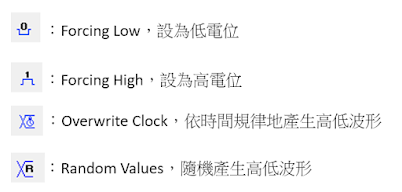

點選邏輯電路的圖示Symbol Tool(如下圖紅圈處),開啟Libraries所在的路徑,primitives目錄下的logic,選擇and2(and表示邏輯閘and,2表示兩條線路)。按下 OK ,就會在底稿上看到游標處有一個and的邏輯閘圖,在所在位置點選後,就會在游標位置產生一個圖。可以繼續移到下一個位置,繼續產生and閘,直到按下 ESC 鍵才停止。

同樣的作法可以增加一個or2邏輯閘, 然後使用正交(Orthogonal )或對角(Diagonal)的線條圖示,將邏輯閘的線條延長,如下圖:

接著要畫輸入和輸出的電路圖,點選圖示區的Pin Tool右方的往下箭頭,可以看到三個選項:Input、Output及Bidirn。點選Input,將圖連接在and及or閘的左方當作輸入。點選Output,將圖連接在and及or閘的右方當作輸出。如下圖。

可以點選紫色的pin_name,改變名稱,以下圖為例,將兩個Input改成I1及I2(我原使用I-1及I-2,但在產生波形圖VWF 時編譯會錯誤,命名時需注意,儘量使用英文及數字,不要使用特殊符號)。右方的Pin_name還沒改成O1及O2。

[繪製區塊圖]

點選邏輯電路的圖示Symbol Tool(如下圖紅圈處),開啟Libraries所在的路徑,primitives目錄下的logic,選擇and2(and表示邏輯閘and,2表示兩條線路)。按下 OK ,就會在底稿上看到游標處有一個and的邏輯閘圖,在所在位置點選後,就會在游標位置產生一個圖。可以繼續移到下一個位置,繼續產生and閘,直到按下 ESC 鍵才停止。

同樣的作法可以增加一個or2邏輯閘, 然後使用正交(Orthogonal )或對角(Diagonal)的線條圖示,將邏輯閘的線條延長,如下圖:

接著要畫輸入和輸出的電路圖,點選圖示區的Pin Tool右方的往下箭頭,可以看到三個選項:Input、Output及Bidirn。點選Input,將圖連接在and及or閘的左方當作輸入。點選Output,將圖連接在and及or閘的右方當作輸出。如下圖。

可以點選紫色的pin_name,改變名稱,以下圖為例,將兩個Input改成I1及I2(我原使用I-1及I-2,但在產生波形圖VWF 時編譯會錯誤,命名時需注意,儘量使用英文及數字,不要使用特殊符號)。右方的Pin_name還沒改成O1及O2。

接著進行編譯,可以按下圖中央上方紅圈處的往右箭頭(Compilation)或按下 Ctrl + L 進行編譯,成功或失敗可以在下方視窗看到結果,如果成功就會看到以下畫面:

到這裡已經完成電路圖的繪製,接著練習如何使用波形檢視結果。

[檢視波形結果]

要檢視邏輯運算的結果,需要新增一個VWF檔,運用波形來看產出的結果為何?例如:0 and 1結果為0...等運算。要建立VWF檔,可選擇[File] → [New],選擇 [University Program VWF],按下 OK 。按下 OK 後出現以下視窗,可在左方紅框處按滑鼠右鍵,選擇[Insert Node or Bus]:

除了使用上述的方法外,還可以在功能選單按下 [Edit] → [Insert] → [Insert Node or Bus],出現下圖中右方的一個小視窗, 按下下圖1的 Node Finder ,出現左方小視窗,按下標示2的 List ,出現稍早編譯好的邏輯圖Input跟Output變數名稱。按下標示3的 >> 將變數加進已選擇的視窗內,按下 OK 回到小視窗,再按一次 OK 。

按下 OK 後出現以下視窗,如要放大或縮小時間間距,可以用 Ctrl + 滑鼠滑輪進行縮放。

設定完成後,要呈現波形的結果,可以在上方選單[Simulation]下拉,選擇[Run Functional Simulation],進入編譯視窗。正常應該會編譯會成功,因我用的是v20.1試用版,第一次執行時,出現以下錯誤畫面:

錯誤說明 -novopt 選項在不久將來要被移除,雖然不知道這是什麼設定?需要修改編譯參數,可以到上方選單[Simulation]下拉,選擇[Simulation Settings],看到以下視窗。將藍色標示的字刪除,按下Save存檔,再次執行 [Run Functional Simulation]就可以成功了。

編譯成功得到的結果如下圖,可以看到 and閘 及 or閘的結果:

張貼留言